UBM化镀

随着半导体封装技术小型化、高密度化之进展,LSI及IC等晶片接合方式由过去打线接合(Wire bonding)转移至覆晶技术(Flip Chip)之制程也逐渐普及, 而在覆晶技术( Flip Chip)当中,以金属Pad与锡球之接合为目的的UBM形成则是不可或缺的一项制程。本公司之UBM代工以无电镀(无电解镀)制程,为兼顾低成本、短交期、小型化,并能善尽环境保护责任之优异制程。

| 种类 | 薄膜材料 |

|---|---|

| 主要产品 | UBM化镀代工服务 |

| 主要基本用途 | LSI、IC等晶片与电路板之接合 |

UBM简介

UBM为Under Bump Metallurgy制程之简称(亦可称作Under Bump Metal或Under Barrier Metal),其将半导体晶圆加以化镀后所形成之金属层(晶圆镀膜),能够赋予晶圆电极上之锡球良好的接合特性。

而使用无电镀(无电解镀)─化学镀(E-less/electroless plating)方式之制程则为本公司UBM代工服务(半导体镀膜)之特色,透过本公司化镍金(NiAu/ENIG)及镍钯金(NiPdAu/ENEPIG)之化镀制程,能有效地在晶圆电极上形成一层金属化镀膜,此外,UBM同时也被广泛地应用于打线接合(Wire bonding)之强化,因此UBM在这方面亦被称为OPM(Over Pad Metal)或FSM(Front Side Metal/正面金属)。

本公司UBM化镀代工之规格

UBM化镀代工服务 规格、特性

| (标准值) | ※过往试作实绩 | |

|---|---|---|

| 晶圆材质 | Si、GaAs(其他材质之晶圆亦可提供服务) | 同左+SiC |

| 晶圆尺寸 | 50~300mmφ(2”~12”) | |

| 晶圆厚度 | 150µm以上(150µm以下请洽本公司) | Min.80um(6”φ) |

| Pad材质 | 纯Al、AlSi、AlCu、AlSiCu、Cu、Au | |

| Pad形状 | 方形、圆形、其他形状 | Min.4µm□ 开口 |

| 晶圆种类 | 逻辑、记忆体、功率电晶体、MEMS等 | |

| UBM | E-less Ni/Au、E-less Ni/Pd/Au(本公司使用无铅、无氰化镀液) |

| Ni(material) | Ni(P 5~10%) |

|---|---|

| Ni膜厚 | 1~5µm:Pad之间有间隔限制 |

| Pd膜厚 | 0.05~0.2µm |

| Au膜厚 | 0.02~0.05µm(Ni/Pd/Au) 0.05~0.10µm(Ni/Au) |

| 膜厚偏差 | ±10%以下(200mmφ) |

UBM化镀代工产线

- ※产线环境等级

- 无尘室级数 Class1000

- 以程式管控之全自动产线

- 在日本、台湾之两大厂房为您提供服务

本公司UBM化镀代工之特色

特色

- 独家研发制程可有效减轻电位差

- 备有各式分析及测量设备

- 12吋晶圆亦可提供服务

本公司现有测量、检测设备

本公司现有分析仪器之一

| 表面形貌分析 | FIB-SEM、FE-SEM、SPM |

|---|---|

| 表面元素分析 | FE-EPMA、FE-AES、XPS |

| 表面官能基分析 | Raman、FT-IR、UV |

| 金属、晶体结构分析 | XRD |

⇒以我们在半导体领域累积之丰富Know how,为您提供表面构造与元素分析服务

以独家研发化镀液为主之制程特色

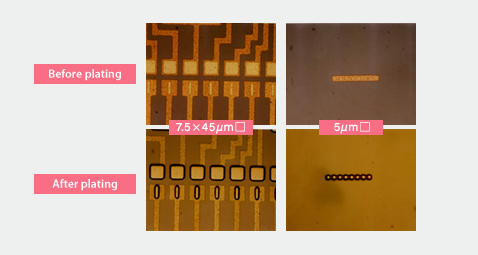

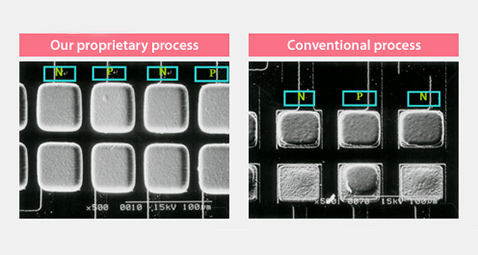

克服IC为人所诟病之电位差、Pad种类与面积差异所导致之高度偏差问题

本公司之UBM化镀代工藉由特别讲究之独家添加剂及化镀方式, 大幅降低Pad电位差、面积差异所导致之高度偏差。

较小Pad亦能均匀化镀

纵使Pad之间电位相异,亦能化镀至几乎同等之膜厚水准

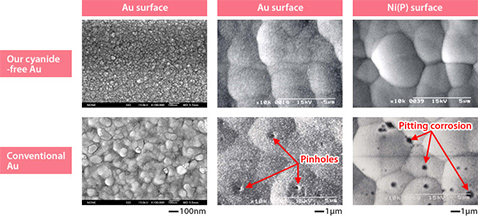

藉由抑制无电解Au化镀之孔蚀,以强化其焊点接合性

本公司之Au化镀液不含氰,并在加入特殊添加剂后相当成功地抑制了Au化镀层之孔蚀,进而确保其良好的焊点接合性,同时我们也将化镀处理液及化镀膜之分析结果反馈至化镀液开发端,借此强化其焊点接合性。

于打线接合(Wire bonding)强度上也能充分展现其可靠度

本公司化镀之功效并不仅止于覆晶技术(Flip Chip)而已,当其作为打线接合(Wire bonding)之Bond Pad 接合面基础时, 也能充分展现其功效。

符合无铅相关环保规范

为善尽环境保护责任,本公司采用不含氰及铅等RoHS规范所明定有害物质之环保药液。

※24小时受理。